VHDL Testbench

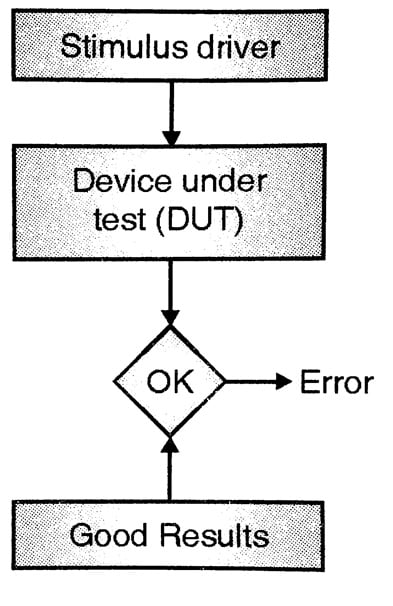

VHDL language is simulators and synthesizers. Sometimes they are not actually downloading behaviour on the chip instead they are generating patterns called VHDL testbenches. A testbench is a VHDL code that is used to check the functionality of a design. Also, outputs can be checked for correct behaviour. The design which allows to verify the […]